ISSN: 2357-0954

DOI:10.21608/EJMTC.2023.204819.1254

## Design of a low noise single-ended sensor interface amplifier for bio-potential applications

## **Original** Article

### **Mohamed Taha and Ahmed Naguib**

Department of Electronic Engineering, Military Technical College, Cairo, Egypt

### **Keywords:**

Chopping technique, flicker noise, low noise, low power, offset, sub-threshold

#### **Corresponding Author:**

Ahmed Naguib, Department of Electronic Engineering, Military Technical College, Email: a.naguib@ieee.org

#### Abstract

This paper discusses a low-noise read-out amplifier circuit for a biomedical sensor interface. The amplifier has two amplification stages with a Miller compensation capacitor that offers high gain with a large output swing. For power efficiency, all transistors are operated in a sub-threshold regime that makes the design suitable for implantable and portable medical devices. The proposed design works at the heart of bio-medical sensor interface circuits. It offers n amplification for different bio-potential signals such as electroencephalogram (EEG), electrocardiogram (ECG), and electromyogram (EMG) according to its bandwidth (BW). Furthermore, a small signal model analysis of the proposed amplifier is presented. A chopping technique is also proposed to reduce the sensor offset voltage and the flicker noise generated from sensor interface circuits. The proposed amplifier design achieves a gain and a BW of 62.16 dB and 506 Hz respectively. The input commonmode range (ICMR) varies from 0.3 V to 0.8 V with a phase margin (PM) of 62.57° at VCM equals 0.3 V and 66.8° at VCM of 0.8 V. The circuit is designed in 130 nm CMOS technology and consumes a power of  $0.4 \mu W$  from 1 V supply. Also, the chopping technique reduces inputreferred voltage noise from 38.445  $\mu$ V/sqrt(Hz) to 3.06  $\mu$ V/sqrt(Hz) within a frequency range from 0.01Hz to 500Hz.

#### 1. INTRODUCTION

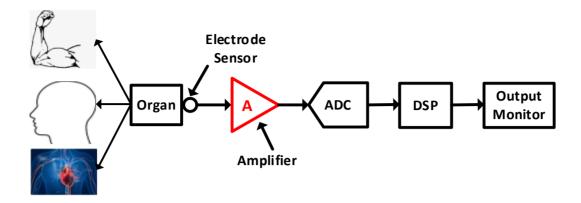

The Op-amp is considered the main building block in any analog integrated circuit. It is commonly used at the front end of bio-medical sensor interface circuits<sup>[1]</sup>. The main role of the amplifier is to amplify the sensed bio-potential signal from the human body to reach a suitable full-scale (FS) level for further signal processing, especially at the low-power analog to digital converter (ADC) input such as successive approximation register (SAR) ADCs<sup>[2,3]</sup>. For instance, the most famous biopotential signals that originate from the human body are: ECG which comes from the Heart activity, EMG arises from the muscles activity, and EEG which results from the activity of the Brain<sup>[4]</sup>. The graphical abstract, depicted in Figure 1, illustrates the process of extracting bio-potential signals from various sources such as the brain, muscles, or heart activity using an electrode interface circuit. The biopotential signal captured by the electrode is subsequently amplified to an appropriate level for further processing in the digital domain. The characteristics of the most famousbio-potential signals are illustrated in more detail as shown in Table 1. As presented, most of these signal amplitudes range from 0.001 - 5 mV and BW from 0.5-500 Hz. Consequently, a lot of design challenges arise when acquiring and amplifying these signals as they all originated from a noisy environment within the human body.

Fig. 1: Block diagram of biomedical system

Table 1: Characteristics of bio-potential signals<sup>[4]</sup>.

| Bio-Potential Signals | Amplitude(mV) | Frequency Range (Hz) |

|-----------------------|---------------|----------------------|

| EEG                   | 0.001 to 0.3  | 0.5 to 100           |

| ECG                   | 0.5 to 4      | 0.01 to 250          |

| EMG                   | 0.1 to 5      | Up to 500            |

For signal amplification, there are many types of operational trans-conductance amplifier topologies such as folded cascode, telescopic cascode, single OTA, and twostage amplifiers. Table 2 illustrates the comparison between these four types in terms of their specifications (DC gain, output swing, CMIR, efficiency, noise, and stability). From Table 2 it can be seen that the two-stage amplifier topology is the best candidate for higher DC voltage gain, larger output swing, and large ICMR, however, this comes with a trade-off with high power dissipation, high Noise, and poor stability. The higher noise, in this case, is mainly because of flicker noise which is a real problem, especially in biomedical applications as it represents the dominant noise source at lower frequencies. There are several techniques available for reducing noise and DC-offset in electronic circuits. One such technique is Correlated Double Sampling (CDS), which is particularly effective in data acquisition systems. CDS minimizes offset errors and reduces noise by subtracting an initial reference sample from subsequent samples. Another technique commonly used for low-frequency noise reduction is Auto-zeroing (AZ). AZ involves periodically measuring and canceling the offset error to improve circuit accuracy. Additionally, the chopping technique is employed to shift noise and offset to higher frequencies. It involves modulating the input signal and using synchronous demodulation to extract the desired signal while rejecting noise.

By utilizing techniques such as CDS, AZ, and chopping,

along with appropriate stability enhancement methods, electronic circuits can achieve enhanced performance and reliability. These techniques are especially valuable in biomedical applications where accurate signal acquisition and processing are crucial. In addition to noise and offset reduction, stability enhancement is crucial in electronic circuits. One method for stability enhancement is the use of a Miller compensation capacitor. This capacitor helps in improving the stability of amplifiers and reducing the risk of instability. Additionally, in certain cases, adding a resistor in conjunction with the Miller compensation capacitor can further enhance stability and reduce power dissipation associated with stability improvement.

Accordingly, this paper proposes different techniques to overcome the aforementioned problems. In this work, all the circuit transistors are designed in the sub-threshold region to achieve higher power efficiency. In addition, the chopping technique is used to overcome the flicker noise and DC offset problems. Furthermore, Miller compensation capacitance is used to get an unconditionally stable design. These solutions are introduced in more detail throughout the paper.

This paper is organized as follows. Section II presents the two-stage amplifier design with Miller capacitance. Section III discusses the chopper circuit integration with the single-ended amplifier design. Section IV provides the simulation results of the proposed amplifier circuit. Finally, Section V concludes the paper.

|       | _  |      |            |

|-------|----|------|------------|

| Table | 2: | OTAs | comparison |

| spec       | Miller | Telescopic | Folded     | 5T OTA  |

|------------|--------|------------|------------|---------|

| DC gain    | V.Good | Good       | typical    | Bad     |

| O/P swing  | V.Good | Bad        | typical    | good    |

| CMIR       | Good   | bad        | V.Good     | typical |

| Efficiency | Bad    | Good       | sufficient | V.Good  |

| Noise      | Bad    | Good       | sufficient | V.Good  |

| Stability  | Bad    | Good       | sufficient | V.Good  |

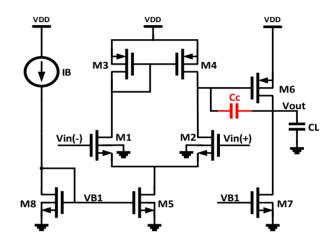

Fig. 2: Block Diagram of Two Stage Amplifier with Miller capacitor

# 2. TWO-STAGE AMPLIFIER DESIGN WITH MILLER CAPACITANCE AND RESISTANCE

The top-level block diagram of the two-stage amplifier with Miller compensation capacitor is illustrated in Figure 2. It consists of two amplification stages and a compensation capacitor CC The first stage (A1) is represented by an

operational Trans-conductance Amplifier (OTA) that contributesmost of the amplifier gain while the second stage (A2) achieves a large output swing

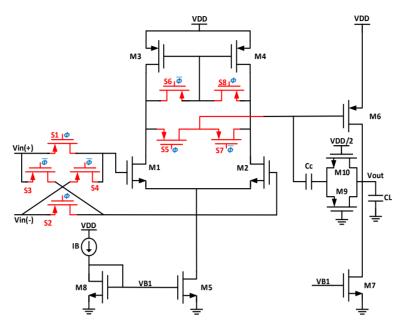

**Fig. 3:** Schematic of CMOS single-ended Two Stage Amplifier with Miller compensation capacitor.

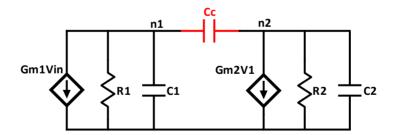

Fig. 4: Small Signal Model of the Two-Stage Amplifier using only compensation capacitance.

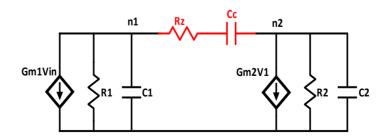

Fig. 5: Small Signal Model of the Two-Stage Amplifier using compensation capacitance and resistance.

The Miller compensation capacitor is inserted in a parallel path between the second stage's input and the output terminal. Figure 3 shows a detailed circuit schematic of a single-ended two-stage differential amplifier with a Miller compensation capacitor. The first OTA stage consists of transistors from M1 to M5. The first two transistors M1 and M2 work as differential input pairs. Whereas M3, which is connected as a diode-connected Transistor, and M4 represent the OTA load. To bias the first OTA stage, M5 works as a current source. The output from the OTA, which is the drain of M4, is connected to the gate of M6 which represents the input of the second stage. On the other hand, the second stage is represented as a common source amplifier with a current source load of M7. The compensation capacitor CC is connected between the gate of M6 and its drain which is also connected to a capacitive load CL<sup>[5]</sup>. From Miller's approximation, a large capacitance can be seen when looking at the input terminal of the second stage. Also, almost the same capacitance is seen locking from the output of the second stage. Miller approximation capacitance significantly affects the design stability as the large capacitance pushes the dominant pole to the left-hand side and the lower capacitance at output approximately maintains the first non-dominant pole at the same value. Accordingly, a good separation between the dominant and first non-dominant pole is maintained which results in increasing phase margin (PM) and thus the stability enhancement of the proposed amplifier. In addition to stability enhancement, miller capacitance reduces the DC offset voltage of the proposed circuit<sup>[6]</sup>. As the design targets ultra-low power consumption, to be suitable for implantable and portable biomedical devices, all amplifier transistors are designed to operate in a subthreshold regime. Accordingly, high power efficiency is

To have an accurate model for the sub-threshold region transistor, let's start with the saturation region model and adapt it accordingly to the sub-threshold case. The equivalent small-signal model for a single transistor working in a sub-threshold region is the same as that of the saturation region, however, the trans-conductance (gm) and output resistance (ro) will be significantly different<sup>[7,8]</sup>. The sub-threshold trans-conductance gm is represented as:

$$g_m = \frac{I_{sub}}{n_n \cdot V_T} \tag{1}$$

Where  $I_{sub}$  is the transistor sub-threshold current,  $n_n$  is the sub-threshold coefficient, and  $V_T$  is a thermal voltage which is given by,

$$V_T = \frac{K \cdot T}{q} \tag{2}$$

Where K is the Boltzmann constant, T is the temperature in Kelvin, and q is the electron charge. While  $n_n$  is represented as,

$$n_n = 1 + \frac{c_{dep}}{c_{ox}} \tag{3}$$

Where  $C_{dep}$  is the depletion-layer capacitance per unit area,  $C_{or}$  is the gate capacitance per unit area.

$$I_{sub} = I_O \cdot e^{\left(\frac{V_{GS} - V_{th}}{n_n V_T}\right)} \cdot \left(1 - e^{\frac{V_{DS}}{V_T}}\right) \tag{4}$$

Where  $V_{th}$  is the sub-threshold voltage.  $I_0$  is given by:

$$I_O = \mu C_{ox} \left(\frac{W}{L}\right) (n_n - 1) V_{th}^2 \tag{5}$$

Where  $V_{th}$  is the threshold voltage. The transistor output resistance is given by,

$$r_o = \frac{1}{\eta * g_m} \tag{6}$$

Where  $\eta$  is the drain-induced barrier-lowering coefficient.

Figure 4 depicts a small-signal model of the proposed design of the two-stage amplifier with Miller compensation working in the sub-threshold regime. Detailed circuit analysis is performed throughout the proposed work to have an accurate small-signal model for the proposed design. By applying and solving KCL equations at nodes n1 and n2, the following transfer function is obtained<sup>[9]</sup>,

$$\frac{V_{out}}{V_{in}} = \frac{G_{m1}G_{m2}R_1R_2\left(1 - \frac{SC_c}{G_{m2}}\right)}{a \cdot S^2 + b \cdot S + 1} \tag{7}$$

Where:

$$\begin{array}{l} {a = }{R_{I}}\,{R_{2}}\left( {{C_{I}}\,{C_{2}} + \left( {{C_{2}} + {C_{I}}} \right)\,{C_{C}}} \right)\\ {b = }\left( {{R_{1}}\left( {{C_{1}} + {C_{C}}} \right) + {R_{2}}\left( {{C_{2}} + {C_{C}}} \right) + {R_{1}}\,{R_{2}}\,{G_{{\rm{m1}}}}\,{C_{C}}} \right) \end{array}$$

Gm1 is the trans-conductance of the first amplifier stage, and Gm2 is the trans-conductance of the second stage. Also, R1 and R2 are the total output resistances of the first and second amplifier stage and equal to  $\simeq r_{02}//r_{04}$  and  $\simeq r_{06}//r_{07}$  respectively. The transfer function formula for a second-order system with zero feedthrough is equal

$$\frac{V_{out}}{V_{in}} = \frac{A_O\left(1 - \frac{S}{\omega_z}\right)}{s^2\left(\frac{1}{\omega_{P_1}\omega_{P_2}}\right) + S\left(\frac{1}{\omega_{P_1}} + \frac{1}{\omega_{P_2}}\right) + 1}$$

(8)

Comparing equations 7 and 8 while making some approximations and reductions, the following formulas can be obtained,

$$\omega_{P1} = \frac{1}{R_1(G_{m2}R_2)C_C}$$

(9)

Where  $\omega P1$  represents the dominant pole, while the non-dominant pole can be written as

$$\omega_{P2} = \frac{G_{m2}}{C_2} \tag{10}$$

The zero feed through due to Cc is derived as:

$$\omega_Z = \frac{G_{m2}}{C_C} \tag{11}$$

Also, the gain bandwidth product equals

$$GBW = \frac{G_{m1}}{C_C} \tag{12}$$

And finally, the DC voltage gain of the amplifier is

$$A_{DC} = G_{m1}G_{m2}R_1R_2 (13)$$

From the derived equations, the zero feed-through of CC needs to be larger than GBW to reduce its effect on the amplifier stability. As a result, Gm2 is selected to be 10 times larger than Gm1 (Gm2 = 10Gm1)<sup>[5]</sup>. Consequently, the PM is then can be expressed as,

$$PM = 84.29 - \arctan\left(\frac{c_2}{10c_c}\right) \tag{14}$$

To further enhance the amplifier stability and reduce power dissipation, another compensation type is presented. Resistance in series with CC compensation capacitor is used. Figure 5 shows an equivalent small-signal model for the proposed design with added compensation resistance. By following the previous steps, a new equation describes the zero feed-throughs can be obtained as follows<sup>[10]</sup>;

$$\omega_Z = \frac{1}{\left(\frac{1}{G_{m2}} - R_z\right) c_C} \tag{15}$$

Resistance  $R_z$  is implemented using a transmission gate to make it almost has a constant value with the input signal. Choosing  $R_z > \frac{1}{G_{mz}}$  shifts the left-hand side zero more to

the left which reduces the effect of the zero on stability and increases the stability margin. The extra PM achieved from using  $R_z$  can be traded off to reduce the power consumption of the proposed design.  $R_z$  can be implemented within the amplifier using a transmission gate as it will be shown in the next section.

Table 3: selected length and W/L ratio for our design

| W/L ratio | length (L) | MOSFET |

|-----------|------------|--------|

| 30        | 300 nm     | M1,M2  |

| 25        | 280 nm     | M3,M4  |

| 2         | 2um        | M5,M8  |

| 240       | 300nm      | M6     |

| 11.5      | 2um        | M7     |

Target design specifications have been achieved throughout the proposed design based on the derived formulas. The amplifier design is done and simulated using the Cadence Virtuoso design environment. Accordingly, Table 3 shows the length and W/L ratio for each transistor in the amplifier circuit. According to the design equations, the Miller compensation capacitor is chosen to be (Cc) = 135 fF. The proposed amplifier circuit achieves a range of specifications based on the common-mode input voltage (VCIM). For instance, it achieves a gain and a bandwidth of 62.16 dB and 561 Hz respectively. The achieved BW covers the frequency range of all bio-Potential signals. The circuit consumes 400 nW of power from a 1 V supply. The input common-mode range (ICMR) varies from 0.3 V to 0.8 V with a phase margin (PM) of 62.57° at VCM equals 0.3 V and 66.8° at VCM of 0.3 V. The input-referred noise is 38.4455 uV/sqrt(Hz) across the frequency range from 0.01 Hz to 500 Hz. This value is considerably large during bio-Potential signals acquisition. The large value of noise concentrates at a very low frequency as it comes from MOSFETs flicker or 1/f noise.

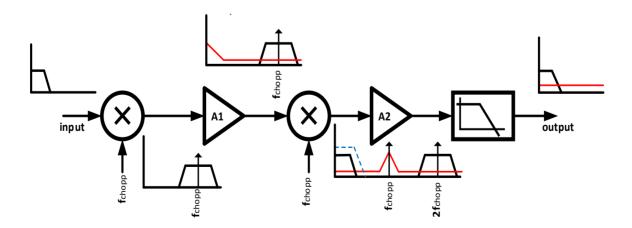

Fig. 6: Block Diagram of chopper circuit

Fig. 7: Schematic of the two-stage differential amplifier with chopper technique

## 3 CHOPPER CIRCUIT IN A SINGLE-ENDED COMPENSATED TWO-STAGE AMPLIFIER

Across bio-potential signals, BW, flicker noise, and DC offset are the most important sources of acquisition errors. To reduce the effect of offset and flicker noise in CMOS amplifiers, the Chopping technique is proposed<sup>[11, 1]</sup>. For a single CMOS transistor, the flicker noise power equals,

$$V_n^2(f) = \frac{K}{C_{OX}WL} * \frac{1}{f}$$

(16)

Where K is the flicker noise coefficient, W is the transistor width, L is the channel length, and COX is the gate oxide capacitance per unit area. The chopping technique is an analog modulation technique that can be applied within the circuit to tackle the offset and flicker noise problems. This can be done using two steps of modulation/demodulation. First, the input bio-potential signal is applied to the first chopper circuit as shown in Figure 6. Consequently, the signal is modulated and shifted to the higher frequency of  $f_{chopp}$ . Next, the modulated signal is amplified along with the amplifier input-referred flicker noise by the gain of the amplifier. Second, another chopper circuit demodulates the amplified bio-potential signal back to the baseband and meanwhile modulates the flicker noise to the higher frequency of  $f_{chopp}$  and its harmonics. A low pass filter is then used to filter out any  $f_{chopp}$  harmonics while passes only amplified input signal without any flicker noise and offset as depicted in Figure 6. While the chopping technique is effective in reducing low-frequency noise and DCoffset, it introduces certain overheads in terms of power consumption and circuit area. These overheads arise from the digital circuitry required to generate the necessary nonoverlapping clocks for modulation and demodulation

processes. Despite these overheads, the chopping technique remains a valuable approach for reducing low-frequency noise and offset. However, designers must carefully evaluate the trade-offs between noise reduction benefits and the associated power consumption and circuit area requirements. Figure 7 shows the transistor level schematic of the two-stage amplifier with the chopper circuit where  $\boldsymbol{\upphi}$  and  $\boldsymbol{\upphi}$  represents a non-overlapping clock from  $f_{\mbox{\tiny chopp}}$ in Figure 6. The chopper circuit itself consists of four transistors S1 - S4 that switch ON and OFF according to the applied clock phase. When the clock is high then S1 and S2 are switched ON and S3 and S4 are switched OFF and the input signal is applied directly to the amplifier input. On the other hand, when the clock is low, S1, S2 are turned off and S3, S4 are turned ON and the input signal polarity is alternated before it appears at the amplifier input. The chopping signals  $\phi$  and  $\overline{\phi}$  are designed as non-overlapping clocks. The second modulation/demodulation circuit is constructed from transistors S5 – S8. It works with the same theory as the first chopper stage; however, it modulates the flicker noise while demodulating the input bio-potential signal<sup>[12]</sup>. The chopper circuit used in the proposed single-ended two-stage amplifier reduces the flicker noise generated from the first amplifier stage, however, the noise from the second stage is not affected. Rz is implemented using a transmission gate which is constructed by M9 and M10 as shown in Figure 7. To maintain fast settling, the chopper transistor switches ON resistance Ron is reduced. It is noted that all N-MOSFET bodies are connected to the ground and the P-MOSFET bodiesare connected to VDD for the whole design. Accordingly, the width and length of the designed chopper transistors are presented as shown in Table 4,

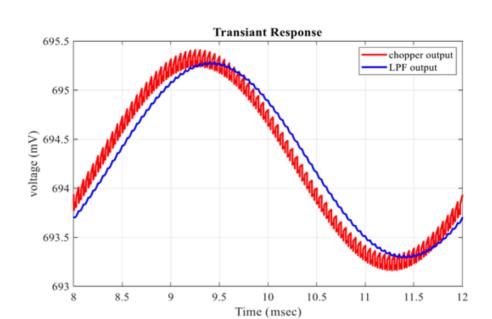

Fig. 8: Transient response of two-stage amplifier with chopper circuit

Table 4: Designed Width and Length of chopper circuit transistor

| MOSFET  | Length (L) | Width (W) |

|---------|------------|-----------|

| S1 – S4 | 120 nm     | 5 um      |

| S5 – S8 | 120 nm     | 160 nm    |

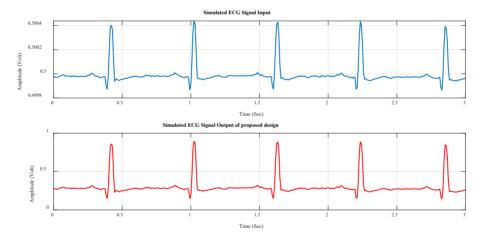

**Fig. 9:** Transient response of ECG signal at  $V_{CM} = 0.5V$

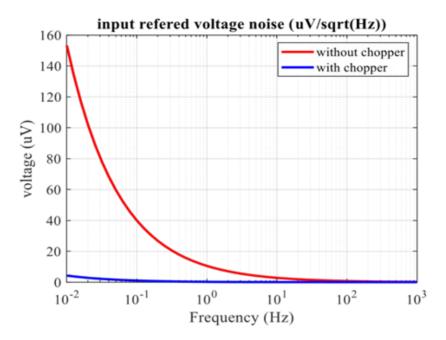

Fig. 10: Simulated input referred voltage noise for the two-stage amplifier with Miller capacitance and other with additional chopper circuit

#### 4. SIMULATION RESULT

The designed circuit is simulated in a Cadence Virtuoso analog environment using UMC 130 nmCMOS technology with a high-speed low threshold voltage transistor model. The transient response of the proposed circuit with the chopper circuit as a response to a sinusoidal signal is illustrated in Figure 8. As shown, after the chopping is

applied, the output signal from the amplifier is spiked due to the harmonic frequency components of the chopper frequency. To get rid of these spikes and higher-order harmonics pass only the signal of interest, a low-pass filter (LPF) is used. To mimic the real amplification of biopotential signals, the proposed circuit is also simulated with a real ECG signal.

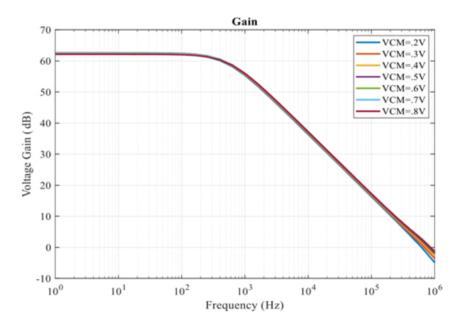

Fig. 11: Simulated voltage gain at common mode voltage from 0.2V to 0.8V

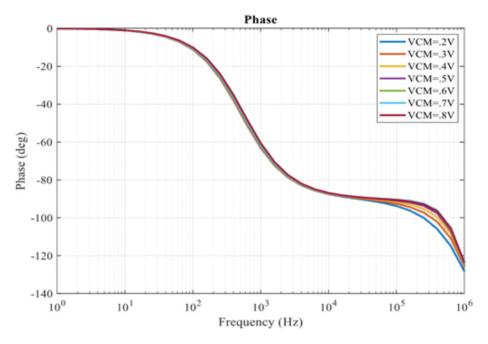

Fig. 12: Simulated phase at common mode voltage from 0.2V to 0.8V

As depicted in Figure 9, ECG signal is applied with 444 uV amplitude (upper curve) and it is amplified by 62 dB of gain at the proposed circuit output (lower curve). The chopping clock frequency fchopp equals 20 KHz is used in the proposed design. Using the chopper technique, the input-referred voltage noise is reduced from 38.4455 uV/sqrt(Hz) to 3.063 uV/sqrt(Hz) across the frequency range from 0.01 Hz to 500 Hz which is a considerable enhancement in the integrated noise as seen in Figure 10.

Figure 10 shows the amplifier voltage gain across frequency at different values of commonmode input voltage from 0.2 V to 0.8 V. Furthermore, Figure 12 shows the proposed amplifier phase response. From the gain and Phase response, it can be deduced that the phase margin (PM) varies from a minimum of 62.57°

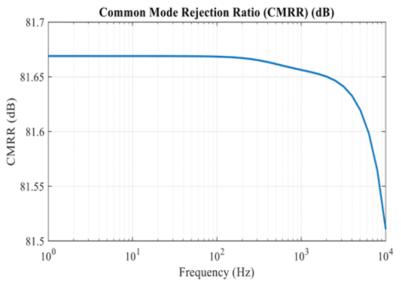

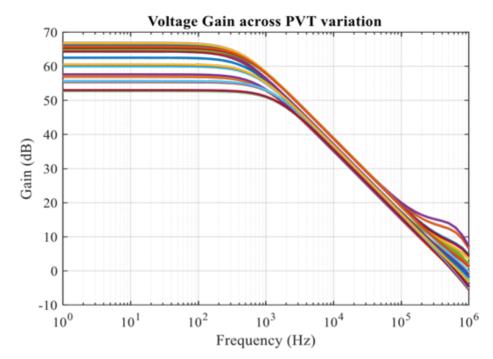

with 3dB bandwidth 566 Hz at VCM equals 0.8 V and a maximum of 66.15° with 3dB bandwidth521 Hz at VCM of 0.4 V. That ensures the amplifie stability for the entire common-mode range. The common-mode rejection ratio is presented in Figure 12 which has a value of 81.654 dB after applying the chopping technique. To test the circuit robustness, Figure 13 illustrates the voltage gain at process corners with a power supply variation of 1 V +/-10% and temperature variation from -40 °C to 85 °C. The circuit shows a DC voltage gain variation from 66 dB to 52 dB. The achieved design performance is listed in Table 5 which shows a comparison with other state-of-the-art designs. As shown in Table V, the proposed design achieves the lowest IRN across the BW of 0.01 HZ to 500 Hz which makes it suitable for bio-potential applications.

Fig. 13: Simulated CMRR for two-stage amplifiers with chopper circuit compensation capacitor and resistor at common mode voltage = 0.5V

Fig. 14: Voltage Gain across Process Corners, 1V%10 of Supply Voltage Variation and different temperature (PVT)

Table 5: Result parameter of our simulation with a comparison with other work

| specification          | This work  | [13]        | [14]       | [15] | [16]  | [17]        | [18]       | [19]       |

|------------------------|------------|-------------|------------|------|-------|-------------|------------|------------|

| power supply (V)       | 1          | 1           | 1.8        | 0.6  | 0.6   | 1.8         | 0.85       | 1.8        |

| DC Gain (dB)           | 62.16      | 55.2        | 45.38      | 86.7 | 39    | 40          | 62         | 34.7       |

| PM                     | 62.57      | 69.46       | NA         | 61.5 | NA    | 61          | NA         | NA         |

| CMIR (V)               | 0.6 V      | NA          | NA         | NA   | NA    | NA          | NA         | NA         |

| technology nm          | 130        | 90          | 180        | 45   | 180   | 180         | 45         | 180        |

| IRN (uv/sqrt(Hz))      | $3.06^{1}$ | $0.138^{2}$ | $1.62^{3}$ | 1820 | 2.3   | $0.031^{4}$ | $3.83^{5}$ | $0.25^{6}$ |

| power dissipation (uW) | 0.4        | 2.6         | 6.25       | 12   | 0.69  | 8           | 1.5        | 4.2        |

| load capacitance (pF)  | 1          | 1           | NA         | NA   | NA    | 10          | NA         | NA         |

| Bandwidth KHz          | 0.505      | 15.3        | 2.9        | 227  | 0.173 | 1           | 0.1        | 0.1        |

| CMRR dB                | 81.65      | 131         | NA         | 129  | 74    | 84          | 176        | 71.5       |

$^1$ IRN over bandwidth from .01 Hz to 500 Hz.  $^2$ IRN at 10 Hz.  $^3$ IRN at 1 Hz.  $^4$ IRN at 1000 Hz.  $^5$ IRN at 10Hz  $^6$ IRN at 100 kHz

#### 5. CONCLUSION

In this paper, a single-ended two-stage differential amplifier with a miller compensation capacitor and resistor is designed. A High gain amplification with a bandwidth up to 505 Hz (which is sufficient for EEG, ECG, and EMG) has been achieved at a low power dissipation of 400 nW. Regarding stability, a good phase margin of 63 deg is achieved. Furthermore, a sub-threshold transistor model for low-power operation is introduced. Also, a chopper technique is introduced to reduce the amplifier's input refereed noise from 38.445 uv/sqrt(Hz) to 3.064 uv/sqrt(Hz) across the bandwidth from 0.01 Hz to 500 Hz.

#### 6. REFERENCES

[1] A. N. Mohamed and H. N. Ahmed, "A low noise CMOS readout front end for mems biopotential sensor applications," in 2014 IEEE 57th International Midwest Symposium on Circuits and Systems (MWSCAS). IEEE, 2014, pp. 868–871.

[2] S. Orguc, H. S. Khurana, H.-S. Lee, and A. P. Chandrakasan, "0.3 V ultra-low power sensor interface for EMG," in ESSCIRC 201743-rd IEEE European Solid State Circuits Conference. IEEE, 2017, pp. 219–222.

[3] A. Naguib, "High speed and low power comparator in 65 nm CMOS for energy efficient biomedical sar ades," in 2020 12th International Conference on Electrical Engineering (ICEENG). IEEE, 2020, pp. 339–342.

[4] M. B. Elamien and S. A. Mahmoud, "Analysis and design of a highly linear CMOS OTA for portable biomedical applications in 90 nm CMOS," Microelectronics journal, vol. 70, pp. 72–80, 2017.

Volume (8) - Issue (1) - Mar 2024

- [5] W. M. Sansen, Analog design essentials. Springer Science and Business Media, 2007, vol. 859.

- [6] Chowdhury, Saidul Alam and Bose, Om Prakash and Hossain, Quazi Delwar, "Design of a two stage cmos operational amplifier in 100nm technology with low offset voltage," in 2018 International Conference on Innovations in Science, Engineering and Technology (ICISET). IEEE, 2018, pp. 56–59.

- [7] S. M. Sharroush, "Analysis of the subthreshold CMOS logic inverter," Ain Shams Engineering Journal, vol. 9, no. 4, pp. 1001–1017, 2018.

[8] S. M. Sharroush, Y. S. Abdalla, A. A. Dessouki, and E.-S. A. El-

- Badawy, "Subthreshold MOSFET transistor amplifier operation," in 2009 4th international design and test workshop (IDT). IEEE, 2009, pp. 1–6.

- [9] B. Razavi, Design of Analog CMOS Integrated Circuits, 1st ed.McGraw-Hill, 2001.

- [10] J. Zhang, "Two-stage operational amplifier design by using direct and indirect feedback compensations," Ph.D. dissertation, Virginia Tech, 2021.

- [11] A. N. Mohamed, H. N. Ahmed, M. Elkhatib, and K. A. Shehata, "A low power low noise capacitively coupled chopper instrumentation amplifier in 130 nm CMOS for portable biopotential acquisition systems, in 2013 International Conference on Computer Medical Applications (ICCMA). IEEE, 2013, pp. 1–5.

- [12] M. Asgari and K.-s. Lee, "A single-ended chopper-stabilized ISFET amplifier for continuous pH measurement applications," in 2015 IEEE 58th International Midwest Symposium on Circuits and Systems (MWSCAS). IEEE, 2015, pp. 1–4.

[13] F. Moulahcene, N.-E. Bouguechal, I. Benacer, and S. Hanfoug,

- "Design of CMOS two-stage operational amplifier for ECG monitoring system using 90nm technology," International Journal of Bio-Science and Bio-Technology, vol. 6, no. 5, pp. 55-66, 2014.

- [14] K. Pratyusha, S. Kumar, and A. Kumari, "Low power amplifier for biopotential signal acquisition system," in 2015 International Conference on Advances in Computing, Communications and Informatics (ICACCI). IEEE, 2015, pp. 324–329.

- [15] G. R. Kumar, K. N. Sunanda, and M. D. Prakash, "An 86 db gain 18.06 my rms input-referred noise lna for bio-medical applications," in Proceedings of the Fourth International Conference on Microelectronics, Computing and Communication Systems. Springer, 2021, pp. 815–824.

- [16] A. Karimi-Bidhendi, O. Malekzadeh-Arasteh, M.-C. Lee, C. M. McCrimmon, P. T. Wang, A. Mahajan, C. Y. Liu, Z. Nenadic, A. H. Do, and P. Heydari, "Cmos ultralow power brain signal acquisition front-ends: design and human testing," IEEE transactions on biomedical circuits and systems, vol. 11, no. 5, pp. 1111–1122, 2017.

[17] A. Adesara and A. Naik, "A low noise low power chopper stabilized

- biopotential amplifier for biomedical applications," International Journal of Computing and Digital Systems, vol. 9, pp. 1-10, 2020.

- [18] P. Jain, S. D. Sharma, A. M. Joshi, and A. M. Joshi, "Design of two-stage differential amplifier with stacked transistors for biomedical applications," Wireless Personal Communications. 28 June 2021.

- [19] S. Chauhan and L. M. Saini, "Low power and low noise instrumentation amplifier," in 2018 Second International Conference on Intelligent Computing and Control Systems (ICICCS). IEEE, 2018, pp. 1332–1335.